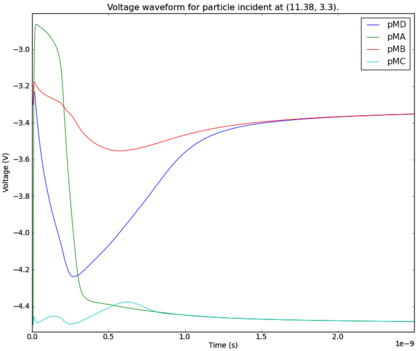

Fig. 2 TCAD simulated voltage waveform of the storage nodes in a DICE flipflop, showing prompt recovery after hit by a heavy ion.

Extensive simulations have been performed at the computing cluster at Cogenda to optimize the layout of circuit cells for SEL immunity and cross-section minimization. Through many design-simulate iterations, hardness is achieved without incurring excessive over-design.

EDA Flow

Cogenda uses an in-house automation flow for cell library creation, and provides a set of vendor-neutal EDA views that can be used in the standard ASIC flow of all major EDA vendors.

| Item | Format |

|---|

| Functional description | Verilog |

| Netlist for LVS | CDL |

| Mask layout | GDSII |

| Synthesis library | Liberty |

| Abstract physical library | LEF |

| Symbol | EDIF |

| Place and routing rules | .tf / .lef |

Cogenda can provide test chip and test keys for radiation hardness tests. A typical design cycle targets a first tape-out in six months.